Using FIFO in Intel platform

Working with FIFOs

1. Overview

There are 3 types of FIFO

- SCFIFO: single-clock FIFO

- DCFIFO: dual-clock FIFO (supports same port widths for input and output data)

- DCFIFO_MIXED_WIDTHS: dual-clock FIFO (supports different port widths for input and output data)

When comparing with Xilinx,

| Intel | Xilinx |

|---|---|

| SCFIFO | Synchronous FIFO |

| DCFIFO | Asynchronous FIFO |

2. Instantiate and configure FIFO

Xilinx has 2 approaches for declaring and configuring FIFO IP core. Intel also provides the same.

a. Megafuntions

Instantiate the library:

LIBRARY altera_mf;

USE altera_mf.altera_mf_components.all;

The VHDL component declaration is located in

< Intel® Quartus® Prime installation directory>eda/fv_lib/vhdl/megafunctions/altera_mf_components.vhd

Here is dcfifo declaration

component dcfifo

generic (

add_ram_output_register : string := "OFF";

add_usedw_msb_bit : string := "OFF";

clocks_are_synchronized : string := "FALSE";

delay_rdusedw : integer := 1;

delay_wrusedw : integer := 1;

intended_device_family : string := "unused";

enable_ecc : string := "FALSE";

lpm_numwords : integer;

lpm_showahead : string := "OFF";

lpm_width : integer;

lpm_widthu : integer := 1;

overflow_checking : string := "ON";

rdsync_delaypipe : integer := 0;

read_aclr_synch : string := "OFF";

underflow_checking : string := "ON";

use_eab : string := "ON";

write_aclr_synch : string := "OFF";

wrsync_delaypipe : integer := 0;

lpm_hint : string := "UNUSED";

lpm_type : string := "dcfifo"

);

port(

aclr : in std_logic := '0';

data : in std_logic_vector(lpm_width-1 downto 0) := (others => '0');

eccstatus : out std_logic_vector(2-1 downto 0);

q : out std_logic_vector(lpm_width-1 downto 0);

rdclk : in std_logic := '0';

rdempty : out std_logic;

rdfull : out std_logic;

rdreq : in std_logic := '0';

rdusedw : out std_logic_vector(lpm_widthu-1 downto 0);

wrclk : in std_logic := '0';

wrempty : out std_logic;

wrfull : out std_logic;

wrreq : in std_logic := '0';

wrusedw : out std_logic_vector(lpm_widthu-1 downto 0)

);

end component;

Note: if using Stratix 10, use_eab = ON is a must.

Looking at signals description here and parameters description here

b. FIFO parameter editor

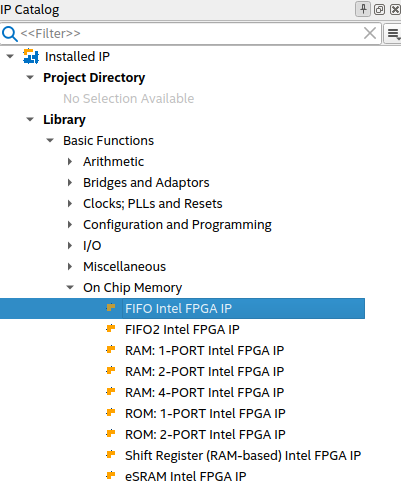

Openning IP Catalog,

Basic Functions > On Chip memory > FIFO intel

There, you can configure your FIFOs. Then, generating IP > Open the HDL file to copy the top module as the component in your design.

c. What are differences?

| Megafunctions | IP Catalog |

|---|---|

| Users must specify timing constraints by themselve. To constraint megafunction FIFO is shown here and here | Timing constraints is automatically generated by the tool. If you are not sure how to constraint the design, this way is recommended. |

3. Important configurations

Clear

Normal vs Show-Ahead mode

4. Example design

http://blogs.plymouth.ac.uk/embedded-systems/fpga-and-vhdl/testing-understanding-the-scfifo-megafunction/

References

- [1] https://www.intel.com/content/www/us/en/docs/programmable/683522/18-0/vhdl-library-use-declaration.html

- [2] https://www.intel.com/content/www/us/en/docs/programmable/683522/18-0/vhdl-component-declaration.html